MAINDEC-8E-D0CC-PB

Adder Test (Binary)

MAINDEC-8E-D0CC-PB

Adder Test (Binary)

MAINDEC-8E-D0CC-D Adder Test (Documentation)

Most of the MAINDEC hardware diagnostic programs do not depend on exact timing and can be run successfully on slow Macintoshs or with the simulated PDP-8/E running as fast as possible. In case of doubt, the MAINDEC passes with the PDP-8/E and the I/O devices set to run with real time speed running on a sufficiently fast Macintosh (that is a 140 MHz Power Mac for the PDP-8/E Simulator 1.x version or a Mac with an Intel Core 2 Duo CPU for the 2.x version).

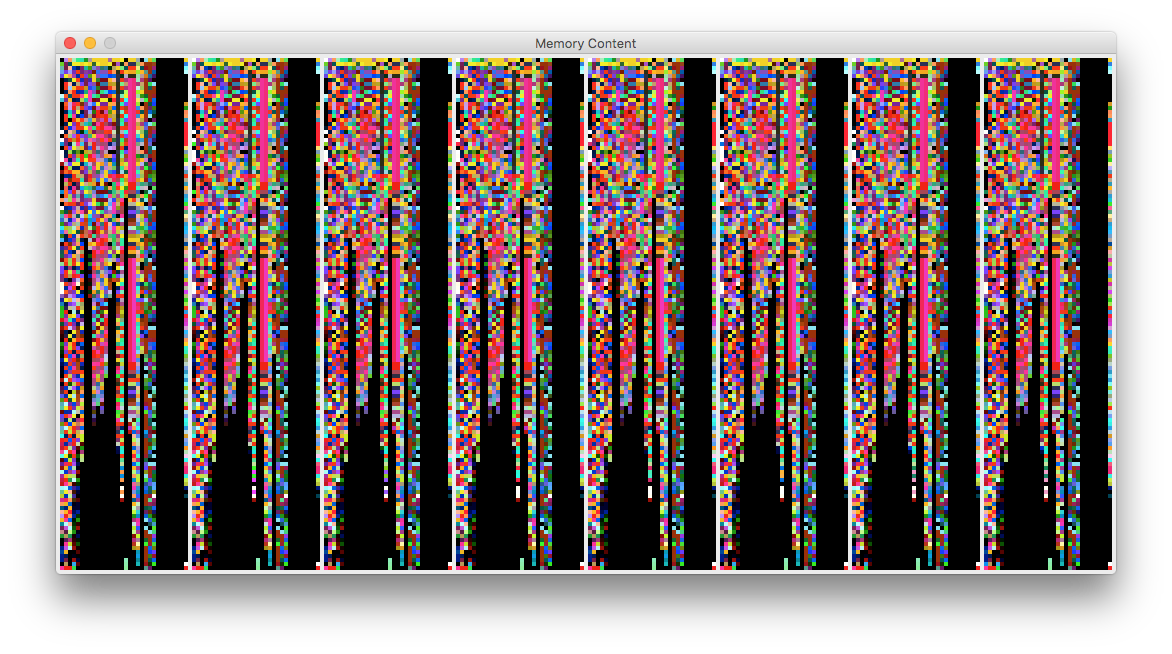

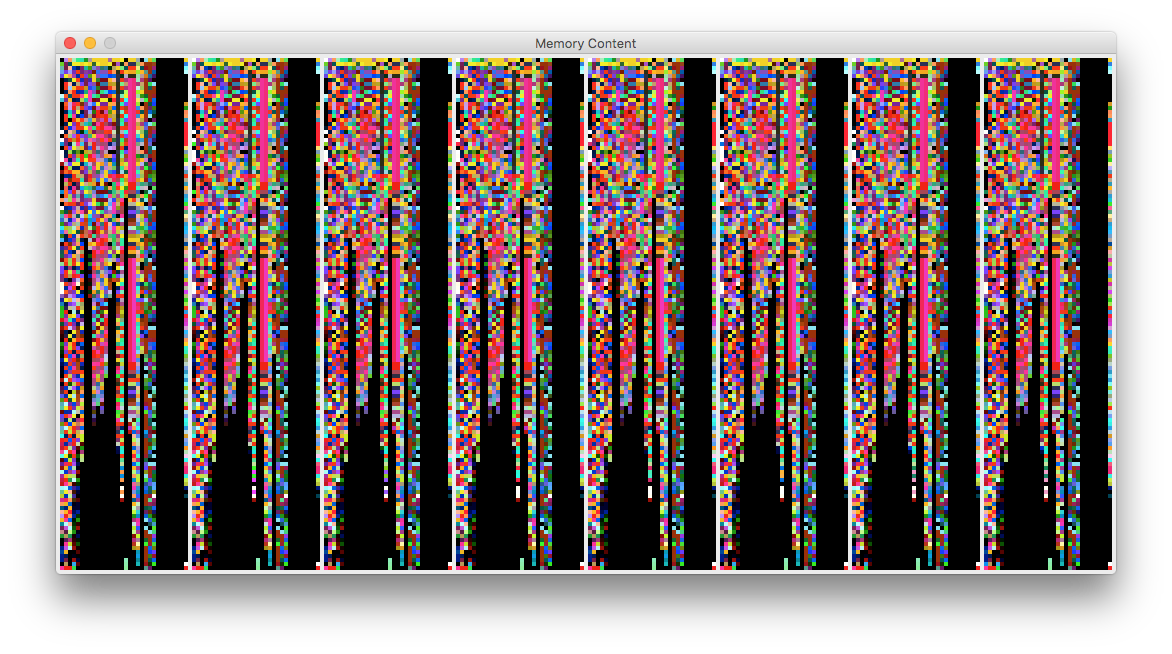

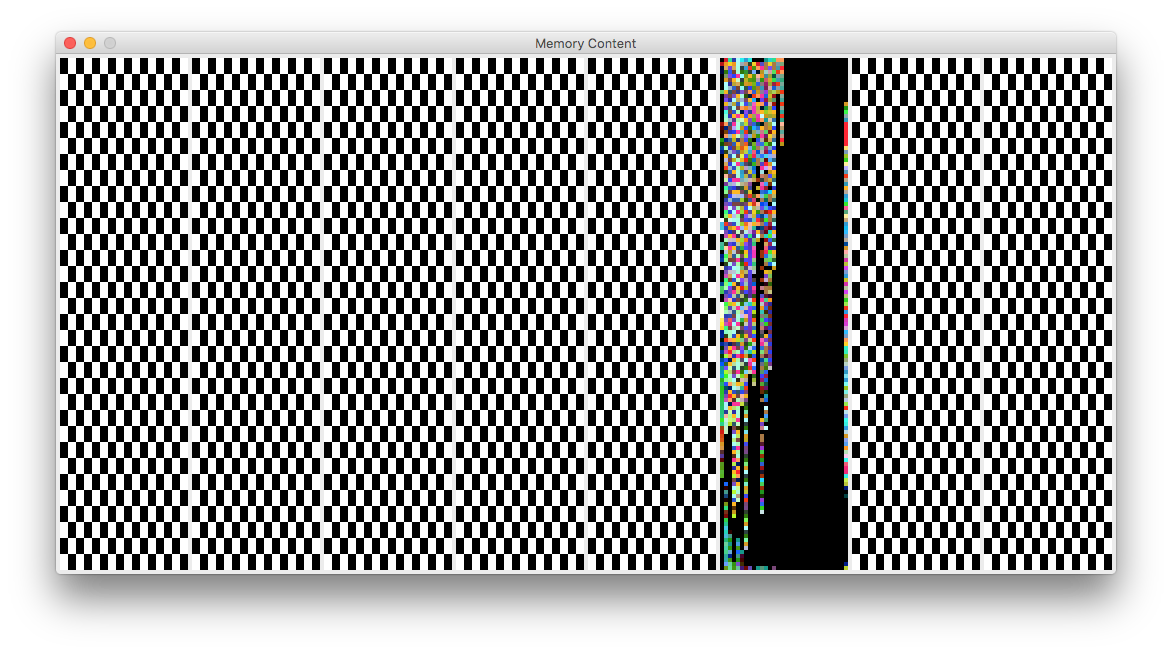

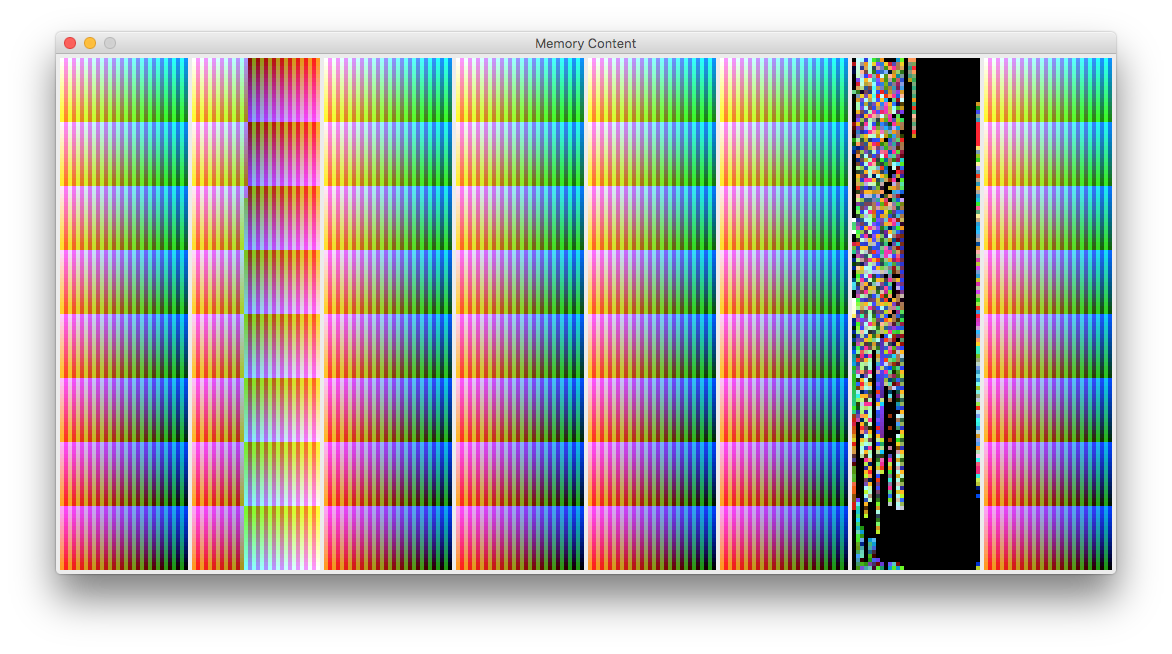

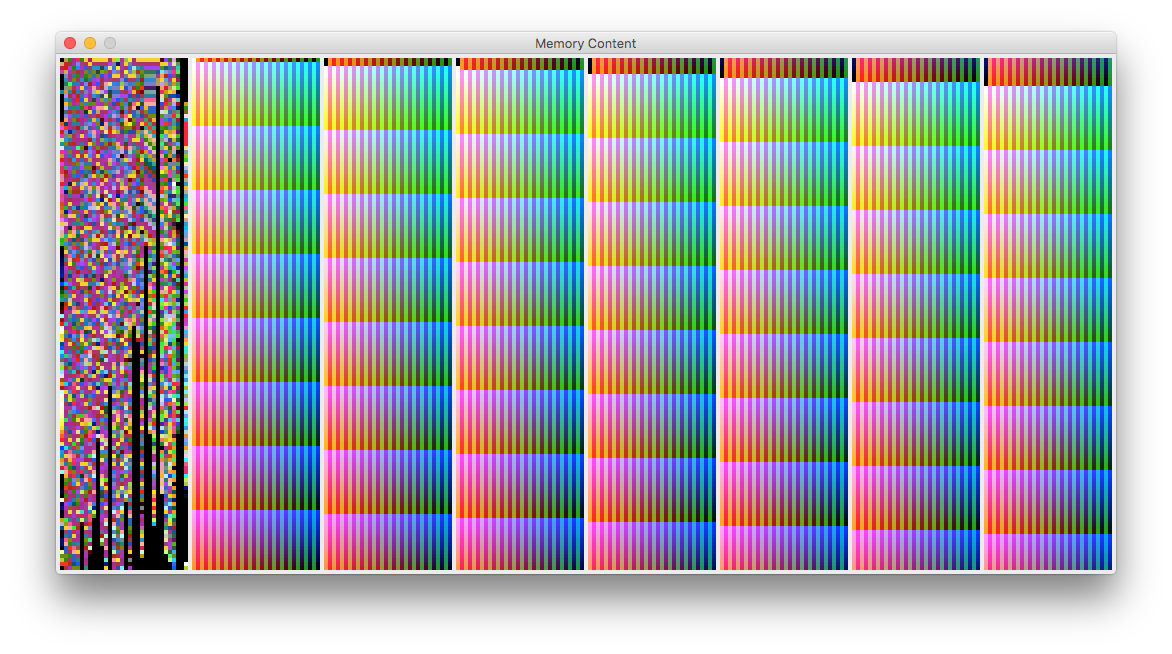

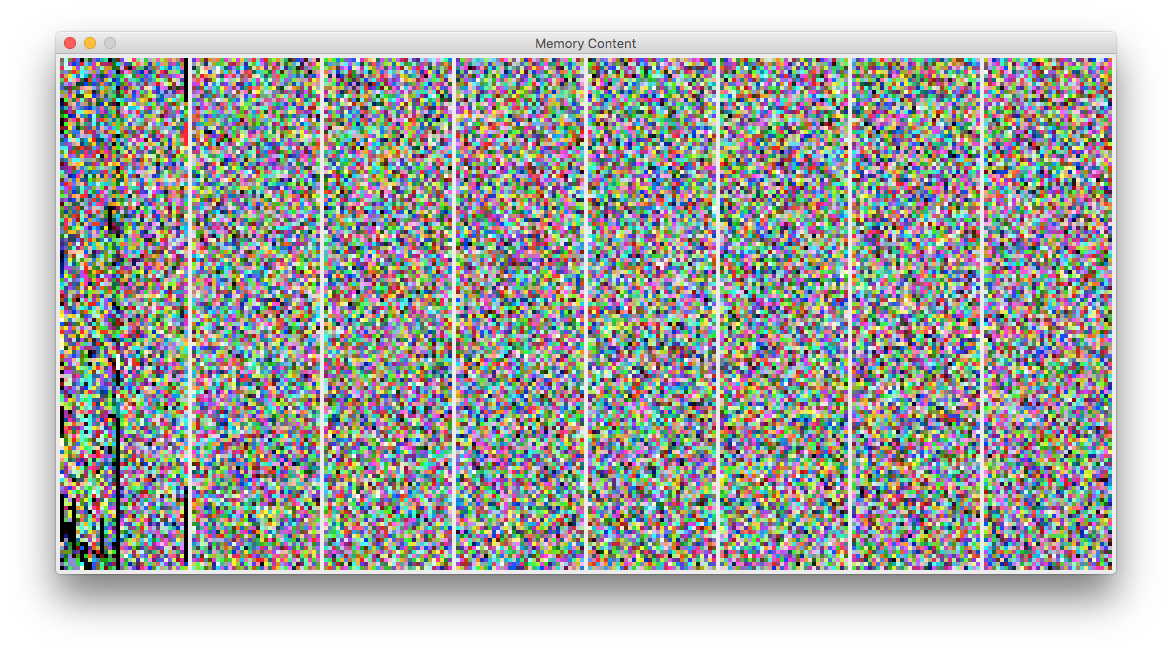

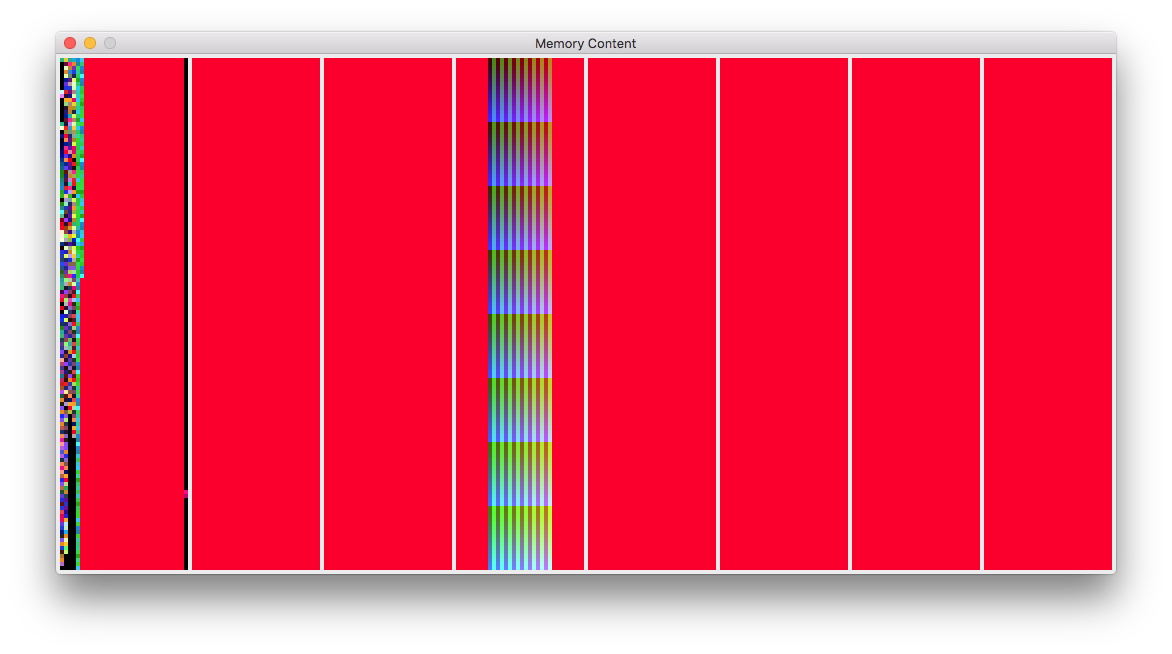

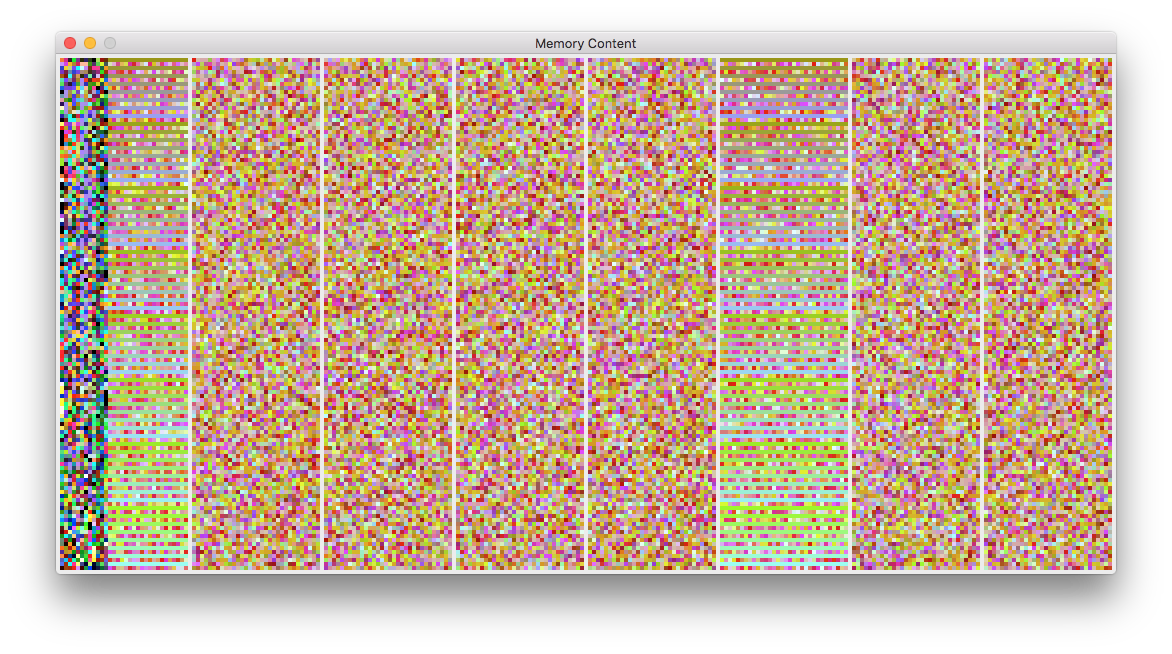

Serval of the hardware diagnostics create pretty patterns in the PDP-8 memory, as seen in the Memory Content plug-in window of the PDP-8/E Simulator. Some screenshots of this window are attached to this page.

MAINDEC-8E-D0BB-PB

Instruction Test Part 2 (Binary)

MAINDEC-8E-D0BB-D Instruction Test Part 2 (Documentation)

MAINDEC-8E-D0CC-PB

Adder Test (Binary)

MAINDEC-8E-D0CC-PB

Adder Test (Binary)

MAINDEC-8E-D0CC-D Adder Test (Documentation)

From a note of Bob Supnik: Start at 0200 with SR=0000. Runs about 35 minutes without any output until the very end (unless error). Then prints as an acceptance indicator on the console:

SIMAD SIMROT FCT RANDOM

MAINDEC-8E-D0DB-PB

Random AND Test (Binary)

MAINDEC-8E-D0DB-D Random AND Test (Documentation)

MAINDEC-8E-D0EB-PB

Random TAD Test (Binary)

MAINDEC-8E-D0EB-D Random TAD Test (Documentation)

MAINDEC-8E-D0FC-PB

Random ISZ Test (Binary)

MAINDEC-8E-D0FC-D Random ISZ Test (Documentation)

MAINDEC-8E-D0GC-PB

Random DCA Test (Binary)

MAINDEC-8E-D0GC-D Random DCA Test (Documentation)

MAINDEC-8E-D0HC-PB

Random JMP Test (Binary)

MAINDEC-8E-D0HC-D Random JMP Test (Documentation)

MAINDEC-8E-D0IB-PB

Basic JMP-JMS Test (Binary)

MAINDEC-8E-D0IB-D Basic JMP-JMS Test (Documentation)

MAINDEC-8E-D0JC-PB

Random JMP-JMS Test (Binary)

MAINDEC-8E-D0JC-D Random JMP-JMS Test (Documentation)

MAINDEC-8E-D1AA-PB

MM8E 4K Memory Checkerboard (Binary)

MAINDEC-8E-D1AB-D MM8E 4K Memory Checkerboard (Documentation)

MAINDEC-8E-D1EC-PB

Memory Address Test (Binary)

MAINDEC-8E-D1EC-D Memory Address Test (Documentation)

MAINDEC-8E-D1GB-PB

PDP-8/E Memory Power On/Off Test (Binary)

MAINDEC-8E-D1GB-D PDP-8/E Memory Power On/Off Test (Documentation)

The PDP-8/E Simulator version 1.3 (or later) passes this test

“better” than a hardware PDP-8/E. After turning off the PDP-8/E

with the power key of the KC8-EA Console, the simulator quits. After

restarting the simulator, you only must operate the continue key of the

console, you need not to load restart address 0201 because the simulator

not only preserves the memory content, but the register content, too.

(With older versions of the simulator, you must save the configuration

explicitly because they do not save the current PDP-8/E state in the

preferences file of the simulator automatically.)

MAINDEC-8E-D1BB-PB

KM8-E 4K Extended Memory Checkerboard (Binary)

MAINDEC-8E-D1BB-D KM8-E 4K Extended Memory Checkerboard (Documentation)

The original documentation is not available. Set SR9-11 to the number of memory fields to check. After each successful cycle, the digit “5” is printed on the teletype. Set SR5 or SR4 to halt the test and set SR3 to avoid relocating of the program.

MAINDEC-8E-D1FB-PB

PDP-8/E Extended Memory Address Test (Binary)

MAINDEC-8E-D1FB-D

PDP-8/E Extended Memory Address Test (Documentation)

MAINDEC-8E-D1HA-PB

PDP-8/E Memory Extension and Timeshare Test (Binary)

MAINDEC-8E-D1HA-D

PDP-8/E Memory Extension and Timeshare Test (Documentation)

Thanks to Willem van der Mark for the scan of his original documentation.

MAINDEC-8E-D0LB-PB

KE8-E EAE Instruction Test Part 1 (Binary)

MAINDEC-8E-D0LB-D

KE8-E EAE Instruction Test Part 1 (Documentation)

MAINDEC-8E-D0MB-PB

KE8-E EAE Instruction Test Part 2 (Binary)

MAINDEC-8E-D0MB-D

KE8-E EAE Instruction Test Part 2 (Documentation)

MAINDEC-08-DHRKA-B-PB

RK8-E Diskless Control Test (Binary)

MAINDEC-08-DHRKA-B-PB

RK8-E Diskless Control Test (Binary)

MAINDEC-08-DHRKA-E-D RK8-E Diskless Control Test (Documentation)

A table for translating the addresses from the listing of the E version documentation to the B version binary.

MAINDEC-08-DHRKB-E-PB

RK8-E Disk Drive Control Test (Binary)

MAINDEC-08-DHRKB-G-D RK8-E Disk Drive Control Test (Documentation)

When PDP-8/E Simulator 1.x runs with PDP-8/E real time speed, this MAINDEC sometimes halts with a STATUS REGISTER ERROR at PC:2054 in TST28, the consecutive sector timing test, or at PC:2132 in TST29, the non-consecutive sector timing test. The tests use a 2.5 ms resp. 40 ms delay loop to check if the READ ALL and WRITE ALL commands are able to act on two consecutive sectors and to check if the READ and WRITE commands need a complete disk revolution (that takes 40 ms) to access consecutive sectors. The internal timing of the simulator is not precise enough to always meet this conditions. The faster the Mac is, the more likely these tests pass. PDP-8/E Simulator 2.x runs this test without any problems.

A table for translating the addresses from the listing of the G version documentation to the E version binary.

MAINDEC-08-DHRKC-H-PB

RK8-E/RK8-L Data Reliability Program (Binary)

MAINDEC-08-DHRKC-H-PB

RK8-E/RK8-L Data Reliability Program (Binary)

MAINDEC-08-DHRKC-H-D RK8-E/RK8-L Data Reliability Program (Documentation)

This MAINDEC runs about 16 hours for a RK8-E with four RK05 drives.

MAINDEC-08-DHRKD-A-PB

RK8-E/RK8-L Disk Formatter Program (Binary)

MAINDEC-08-DHRKD-D-D RK8-E/RK8-L Disk Formatter Program (Documentation)

MAINDEC-08-D3BC-PB

TC01 Basic Exerciser

MAINDEC-08-D3BB-D

TC01 Basic Exerciser (Documentation)

MAINDEC-08-D3EB-PB

TC01 Extended Memory Exerciser

MAINDEC-08-D3EB-D

TC01 Extended memory Exerciser

MAINDEC-08-D3RA-PB

DECTREX 1 TC01 Random Exerciser

MAINDEC-08-D3RA-D

DECTREX 1 TC01 Random Exerciser (Documentation)

Thanks to Volker Hermann for providing the scan of the DECTREX 1 documentation and thanks to Vincent Slyngstad for hosting it on his site.

DEC-08-EUFB-PB

TC01-TU55 DECtape Formatter

DEC-08-EUFB-D

TC01-TU55 DECtape Formatter (Documentation)

The DECtape Formatter is very time-critical. Even when the timing precision of the PDP-8/E Simulator is set to a small value, not every run of the formatter succeeds with a correctly formatted DECtape.

This is the PC8-E Diagnostics restored by Willem van der Mark, the original DEC version is available on his tests page, too.

To run it, three test tapes

MAINDEC-00-D2G1,

MAINDEC-00-D2G2 and

MAINDEC-00-D2G4 are required.

This test only runs with PDP-8/E Simulator 2.x, not with the old 1.x version.

With PDP-8/E Simulator 1.x, for all kinds of real time clocks,

this MAINDEC halts at various tests because the timing resolution

of the simulator is not precise enough to match the clock frequencies.

PDP-8/E Simulator 2.x passes this MAINDEC for all clock speeds.

(In case of doubt, a fast multi-core Mac passes the timing tests better when

all but two cores are turned offline using the “cpuctl” utility.)

PDP-8/E Simulator 2.x only has the clock of the DKC8-AA I/O option board, so it only passes the Real Time Clock Timing Test (section 4.6).

The Control Logic Test 1 regularly fails in the tests CTL3-DILX and CTL3-DILY because the timing resolution

of the simulator is not precise enough to always match the 21 µs delay loop that is repeated many times

during the tests.

Tests 15–17 seem not to be prepared to work with two screens, e. g. the Color Alignment Test 17

for the VR-20 draws the green cross on the first VR-20 and the red cross on the second VR-20.

The binary can be found on the ETOS system disk and the documentation in the

ETOS manuals, see here.

| Bernhard Baehr | 03.04.2026 10:50:00 |